Understanding the Cell Microprocessor

by Anand Lal Shimpi on March 17, 2005 12:05 AM EST- Posted in

- CPUs

Manufacturing, Die Size and Clock Speed

Intel's superiority in manufacturing is responsible for the majority of their technological advances in microprocessors over the past decade, and it's often argued that there isn't a company around that could come close to matching Intel's manufacturing abilities - with the exception of IBM.The Cell prototype boasts some pretty major manufacturing specs:

- 90nm SOI manufacturing process

- 221 mm2 die area

- 234M transistors

- > 4GHz observed clock speed

When it was first announced, the chip sounded massive, but its specifications compare extremely well to Intel's upcoming Pentium D processor; let's take a look at its vitals:

Intel Pentium D Processor

- 90nm strained silicon manufacturing process

- 206 mm2 die area

- 230M transistors

- 2.8GHz - 3.2GHz clock speed

With a slightly larger chip and a few million transistors more, Cell is supposed to be able to run at a minimum of 25% higher clock frequency than Intel's forthcoming Pentium D. We'll let that sit in for a moment...

Dynamic Logic

At first glance, a 90nm SOI Cell running at between 3 - 5GHz looks extremely impressive. After all, the fastest 90nm CPU IBM currently produces runs at 2.5GHz, not to mention that even Intel, the king of clock speed, can't mass produce anything faster than 3.8GHz on their 90nm process. But let's dig a little deeper.The Pentium 4 has two ALUs that run at twice its internal clock speed - so in the case of a Pentium 4 660, that means that two of the more frequently used execution units operate at 7.2GHz - on a 90nm process. So, it's possible to get circuits to run at higher clock speeds, even in the 3 - 5GHz range, on current 90nm processes - it just takes a little bit of creative logic design.

It's been confirmed that Cell is using some sort of dynamic logic as opposed to static CMOS in order to control transistor counts and improve operating frequencies. Intel uses a number of specialized logic techniques in their double-pumped ALUs to reach their 7GHz+ operating frequencies, and Intel has discussed techniques that are similar to the dynamic logic used in Cell.

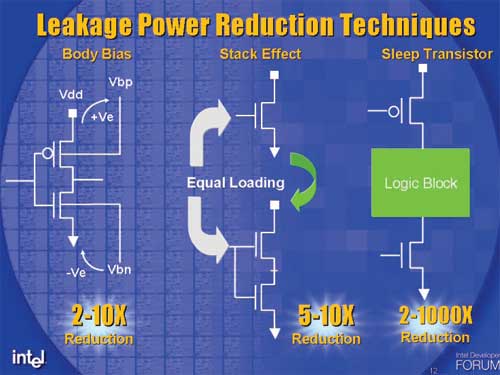

The diagram on the right of a "sleep transistor" should look very familiar by the end of this article

Transistors and You

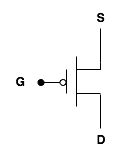

Just about any AnandTech reader who has followed our CPU articles has heard us count transistors before, but understanding how transistors work is quite critical to understanding how IBM can talk about 3 - 5GHz clock speeds for Cell.We'll spare you the details about how transistors are made and the physics behind them in an attempt to keep this section as brief, but as informative, as possible. It's quite common to refer to a transistor as a "switch" much like a light switch, so how does a transistor function like a switch? Below, we have a representation of a p-type transistor:

The input to the gate of the p-type transistor is what makes it function as a switch. If you apply the right voltage to the gate, thus making it a logical "1" or high, current doesn't flow in the transistor. If you don't apply any voltage to the gate, current can flow. Just like a light switch, flip it one way and the light turns on; flip it another and you're in the dark.

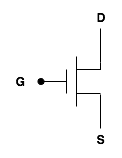

There's another type of transistor that we'll be talking about here: the n-type transistor:

CMOS circuits work by using pairs of n- and p-type transistors (that's where the Complementary element of CMOS comes from). CMOS circuits are by far the most predominant in modern day microprocessors, but as you will soon see, that doesn't mean that they are without flaws.

70 Comments

View All Comments

scrotemaninov - Thursday, March 17, 2005 - link

#23: True, but I believe that when the SPE's access the outside memory they go through the cache. Sure it's a lower coherancy than we're used to but it's not much worse.Houdani - Thursday, March 17, 2005 - link

18: Top Drawer Post.20: Thanks for the links!

fitten - Thursday, March 17, 2005 - link

"Given the speed of the interconnect and the fact that it is cache-coherant,"Only the PPC core has cache. The individual SPEs don't have cache - they have scratchpad RAM.

#22: I believe the PPC core is a dual issue core that just happens to be 2xSMT.

AndyKH - Thursday, March 17, 2005 - link

Great article.Anand, Could you please clarify something:

I had the impression that the PPE was a SMT processor in the sense that it had to be executing 2 threads in order to issue 2 instructions per clock. In other words: I didn't think the PPE control logic could decide to issue 2 instructions from the same thread at any given clock tick, but rather that it absolutely needed an instruction from each thread to issue two instructions.

After reading the article, I don't assume my impression is right, but a comment from you would be nice.

As I come to think about it, my impression is rather identical to 2 seperate single thread in-order cores. :-)

Koing - Thursday, March 17, 2005 - link

Cell looks VERY interesting.Any of you guys seen Devil May Cry 3 on the PS2? Looks great imo same with T5 and GT4.

Cell at first will be tough like most consoles. BUT eventually THE developers will get around it and make some very solidly good looking games.

Lets hope they are innovative and not just rehashed graphics and nothing else.

Thanks for the great article.

Koing

scrotemaninov - Thursday, March 17, 2005 - link

I really hate just dumping loads of links, but this basically is the available content on the CELL.http://arstechnica.com/articles/paedia/cpu/cell-1....

http://arstechnica.com/articles/paedia/cpu/cell-2....

http://realworldtech.com/page.cfm?ArticleID=RWT021...

http://www.blachford.info/computer/Cells/Cell0.htm...

http://www.realworldtech.com/page.cfm?ArticleID=RW...

http://www.hpcaconf.org/hpca11/papers/25_hofstee-c...

http://www.hpcaconf.org/hpca11/slides/Cell_Public_... (slides)

mrmorris - Thursday, March 17, 2005 - link

Brilliant article, there are few places for in-depth hardcore technology presentations but Anandtech never fails.scrotemaninov - Thursday, March 17, 2005 - link

Real concurrency is hard to do for the programmers. It's a real pain to get it right and it's hard to debug. Systematic analysis just gets too complex as there are just too many states, you end up with a huge graph/markov-model and it's just impossible to solve it tractably.Superscalar and SMT just try to increase ILP at the CPU level without burdening the programmer or compiler-writer. However, we've pretty much come to the end of getting a CPU to go faster - at 5GHz, LIGHT travels 6cm between clocks, and an electic PD will travel slower. As it is, in the P4 pipeline, there are at least 2 stages which are simply there to allow signals to propogate across the chip. Clearly, going faster in Hz isn't going to make the pipeline go faster.

So the ONLY thing that they can do now is to put lots of cores on the same chip and then we're going to have to deal with real concurrency. IBM/Sony are doing it now with CELL and Intel will do it in a few years. It's going to happen regardless. What we need is languages which can support real concurrency. The Java Memory Model is an almost ideal fit for the CELL, but other aspects don't work out so well, maybe. We need Pi-calculus/Join-calculus constructs in languages to be able to really deal with these cpus efficiently.

Your comments about CELL not being general purpose enough are a little wrong. IBM /already/ has the CELL in workstations and are evaluating applications that will work well. Given the speed of the interconnect and the fact that it is cache-coherant, I think we'll be seeing super-computers based on many CELLs, it's an almost ideal fit (as it is, you've almost got ccNUMA on a single chip). Also, bear in mind that this is IBM's 5th (or 6th?) generation of SMT in the PPE - they've been at it MUCH longer than Intel - IBM started it in the mid-90s around the same time that the Alpha crew were working on the EV8 which was going to have 8-way thread-level parallelism (got canned sadly).

Also, if you look at IBMs heavy CPUs - the POWER5, that has SMT and dispatches in groups of 8 instructions, not the 3/4 that AMD/Intel manage.

What I'm saying here, is that sure, the SPEs don't have BPTs of BTBs, they're all 2-way dispatch and not greater, but, they all run REALLY fast, they have short pipelines (so the pain of the branch misprediction won't be so bad), and, IBM have had software branch prediction available since the POWER4, so they've been at it a few years and must have decided that compilers really can successfully predict branch directions.

Backwards compatibility doesn't matter. Sure, Microsoft took several years to support AMD64 but that didn't stop take up of the platform - everyone just ran Linux on it (well, everyone who wanted to use the 64bit CPU they'd bought). It'll only be a few months after the CELL is out that we'll have to wait until Linux can be built on it. 100quid says Microsoft will never support it.

Frankly, considering that it's far more likely to go into super-computer or workstation environments, no one there gives a damn about backwards compatibility or Windows support. No one in those environments /wants/ a damn paper clip.

Reflex - Thursday, March 17, 2005 - link

#14: Replace 'lazy developers' with 'developers on a budget' and you will have a true statement. Its not an issue of laziness, its an issue of having the budget to optimize fully for a platform.GhandiInstinct - Thursday, March 17, 2005 - link

Wow Super CPU and SUPER RAMBUS? AHHHH!This will replace my computer. PS3 that is.