AMD's Phenom Unveiled: A Somber Farewell to K8

by Anand Lal Shimpi on November 19, 2007 1:25 AM EST- Posted in

- CPUs

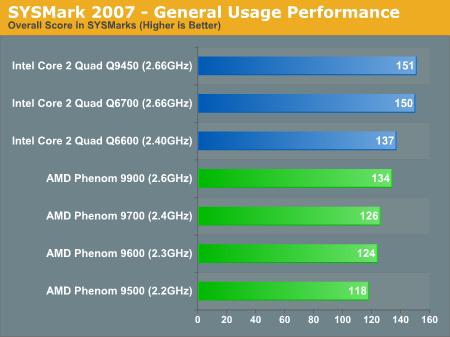

General Application Performance

Right off the bat the numbers aren't looking good for AMD. The Phenom 9600 is priced closest to the Core 2 Quad Q6600, but unfortunately for AMD the Q6600 outperforms it by a healthy 10%. AMD needs a 2.6GHz Phenom to equal the performance of the Q6600, but the 9900 won't be out until next year, when it'll have to face the Penryn based Q9450 and Q9300.

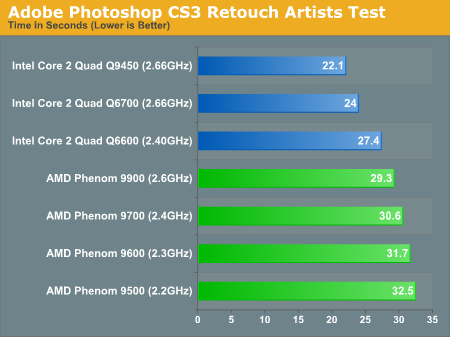

2D Image Manipulation Performance

Once again we broke out the Retouch Artists Photoshop CS3 benchmark, timing a handful of image manipulation operations in CS3:

The Core 2 Quad Q6600 is around 6% faster than the Phenom 9900, 10% faster than the Phenom 9700, and almost 16% faster than the Phenom 9600 which is its closest price competitor throughout the rest of 2007.

124 Comments

View All Comments

Proteusza - Monday, November 19, 2007 - link

Actually, there is every possibility that he is right.First off, how much do you know about instruction sets and compilers? I'm going to assume nothing. If you do know something, then consider this for the edification of other readers.

Compilers take code written in one language and produce an output in another. Specifically, compilers take code written in a language that can be easily understood by humans (ie C++) and output code that a machine can understand (machine code, or bytecode in the case of a JVM).

Now, the problem with enhanced instruction sets, like SSE4, and SSE4.1 and SSE4a, is that they require compiler support. Imagine an instruction set as a vocabulary. And compilers are the programs that produce books, using a specified vocabulary. Now, the simple truth is that Intel makes extra effort to get its vocabulary into use. Thus, Cinebench was most likely compiled with Intel's latest vocabulary, and not AMD's.

So, part of the K10 update was that it allowed SSE operations to be completed much faster, and I'm presuming this requires the use of its new instruction set. If so, that means that Cinebench was basically running in K8 mode.

Not so far fetched, just means AMD has to make sure people update their code. The instruction set issue is another reason why RISC CPU's are generally simpler and faster.

JumpingJack - Monday, November 19, 2007 - link

Look... it is code, that is all ... AMD and Intel are both designing to the same code base, run it on one... then run it on the other... which is faster?Architectural jargon of IMC and victim L3 cache, and x-bit look up ... if it doesn't work it doesn't work.

Kiijibari - Monday, November 19, 2007 - link

Lol .. just code ... imagine a guy talking in a south west Chinese dialect to you. You do not understand anything ? Well .. it is just a language ... ;-)No offense intended: Please do some read up on compliers and programming languages .. it is interesting :)

cheers

Kiiji

Brunnis - Monday, November 19, 2007 - link

Acutally, there shouldn't be any code modifications needed to make use of the new SSE functionality. The difference is internal to the CPU, meaning that it now processes SSE instructions without splitting them. The instructions used are the same as before.That said, there may be untapped potential in the CPU that can be uncovered by the use of a different compiler (due to other reasons). Though, as far as I know, Intel compilers often produce faster code even for AMD CPUs...

About the "architectural advantage" Anand mentioned: Of course the Core 2 has an architectural advantage. It's pretty obvious from the fact that it performs faster, clock-for-clock, in almost all cases while having much higher frequency potential. Not even AMD's integrated memory controller can raise the computational efficiency of their CPU enough to really challenge Intel. AMD may have a more elegant external design and interface to the rest of the system (native quad, HyperTransport, integrated memory controller), but Intel obviously has the more refined internal design. Sadly for AMD, a computational advantage seems to weigh heavier than a neat system/core interface in this case.

Kiijibari - Monday, November 19, 2007 - link

Yes I know what you mean, the SSE instructions are the same, they are just executed faster (in 1 clock compared to 2 clocks before). That is correct, however I wonder how much code is out there that is compiled with the old Intel compilers until 9.X.The problem with these compilers were, that they did not executed the SSE2 codepath on AMD chips, even if the CPU would have been capable of executing it. Instead a slower FPU code is used for AMD K8s.

The newest Intel 10 Compilers have now new compiler flags that can generate SSE2 code for non-intel CPUs, however I did not have seen benches of these so far.

Even the M$ Compiler had some nasty SSE disable "features":

http://einstein.phys.uwm.edu/forum_thread.php?id=6...">http://einstein.phys.uwm.edu/forum_thread.php?id=6...

All in all, I guess there are a lot of programs out there that disable SSE on AMD CPUs :( Therefore a plain compile test of several open-sorce prgorams with gcc / Sun / Pathscale compilers would be nice. Intel CPUs could be benched with Intel compiler, too, any CPU should gets it best code.

cheers

Kiiji

Kiijibari - Monday, November 19, 2007 - link

Yet another wise guy knowing nothing ...Lets imagine an English native speaker ... would he understand Spanish ? No, not much ... but maybe his fried, who learned Spanish in school is better in speaking Spanish, nevertheless, he wont be as good as a native Spanish speaker ...

Who would be the guy with the "superior, best language capabilities" now? The Spanish, the English speaking guy, or his friend ?

Think about it a little bit I am curious about your reply ^^

cheers

Kiiji

MrKaz - Monday, November 19, 2007 - link

“AMD couldn't simply get enough quantities of the Phenom at 2.4GHz to have a sizable launch this year (not to mention a late discovery of a TLB error in the chips),…”I’m very interested in the bug you talked Anand.

Could you say if you know how it affects the CPU:

-Performance?

-Clock speed?

-Slow northbridge clocks?

Or the bug no longer exists in these CPUs?

Complete disappointment.

At least AMD release the 790 motherboards so I can at least put my old CPU on that system with two Ati 3850 cards… ;)

Spoelie - Monday, November 19, 2007 - link

The bug freezes the system at high workloads. It shouldn't have any performance impact.I'm extremely disappointed with phenom, I was planning to get the entire spider platform for my yearly upgrade cycle, but that seems to be a bad idea.

fitten - Monday, November 19, 2007 - link

I would think that transitioning from a running, working system into a brick (not running and not working) would be a fairly significant performance impact ;)

Viditor - Monday, November 19, 2007 - link

I'm waiting for the review on Quad-Crossfire first...

I figure I can get 4 x 3850s for about the same price as an 8800 Ultra. The question is, is it worth it?

If XfireX is good, then I will pull the trigger on 4 x 3850s (or 3870s if I can get them before Xmas), a 790FX mobo, and probably a Phenom 9500...

Then I'll upgrade the Phenom in March when the B3s finally come out.