The Nehalem Preview: Intel Does It Again

by Anand Lal Shimpi on June 5, 2008 12:05 AM EST- Posted in

- CPUs

The Return of Hyper Threading

While Nehalem is designed to scale to up to 8 cores per chip, each one of those cores has the hardware necessary to execute two threads simultaneously - yep, it's the return of Hyper Threading. Thus our quad-core Nehalem sample appeared as 8 logical cores under Windows Vista:

Four cores, eight threads, all in a desktop CPU

Note that as in previous implementations of Hyper Threading (or other SMT processors) this isn't a doubling of execution resources, it's simply allowing two instruction threads to make their way down the pipeline at the same time to make better use of idle execution units. Having 8 physical cores will obviously be faster, but 8 logical (4 physical) is a highly power efficient way of increasing performance.

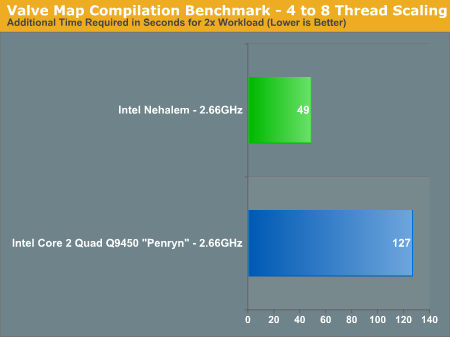

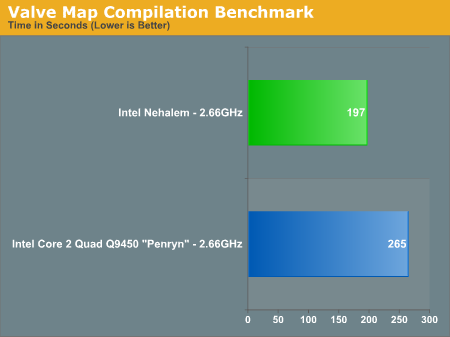

We took Valve's source-engine map compilation benchmark and measured the compile time to execute one instance (4 threads) vs. two instances of the benchmark. The graph below shows the increase in compilation time when we double the workload:

While the 2.66GHz Core 2 Quad Q9450 (Penryn) takes another 127 seconds to execute twice the workload, the 2.66GHz Nehalem only needs another 49 seconds. And if you're curious, this quad-core Nehalem running at 2.66GHz is within 20% of the performance of an eight-core 3.2GHz Skulltrail system. Equalize clock speed and we'd bet that a quad-core Nehalem would be the same speed as an 8-core Skulltrail here. The raw performance numbers are below:

We couldn't disable Hyper Threading so we reached the limits of what we were able to investigate here.

108 Comments

View All Comments

SiliconDoc - Monday, July 28, 2008 - link

lol- Buddy you are thinking.magreen - Thursday, June 5, 2008 - link

Thanks for the amazing preview, Anand!I hope you and Gary will get us more Nehalem information quick like bunnies.

yottabit - Thursday, June 5, 2008 - link

Great Article Anand! I'm so excited for this new technology. But that socket and triple channel memory archetecture makes me want to puke in my mouth a little bit. It's very reminiscent to me of the Socket 423/RDRAM era. I have the feeling that they are going to release this setup for a lot of the early adopters and then screw them over by dropping the socket completely, when they decide that Dual Channel DDR3 is fast enough. I can't picture two platforms running side by side, with two entirely different sockets. People whant a Nehalem but need 4 gigs of ram will end up buying 6 Gigs of ram... and DDR3 ain't exactly cheap.I wish they had plans to through this into the mainstream faster. I'd love to have one of these, in dual channel variety. I'm still running an old early A64, and I'm holding out for these next gen processors in the next year or two.

Its awesome to see that nice performance per clock increase, but the triple channel memory is a real slap in the face to me. Its like Intel saying "look, we increase clock for clock performance, but we also decided to use some brute force and raise our power consumption and motherboard complexity for no reason by adding another impractical memory channel". I don't see it as elegant at all. I think they are overcompensating for their lack of memory bandwith in recent times. :-

Maybe AMD will have a chance to jump in with some nicer Phenom's before Nehalem comes out and actually capture some quad core market?

npp - Thursday, June 5, 2008 - link

I'm tired of all those people who just can live with the fact that the world is spinning and the CPUs that were reviewed here are simply far faster than the Penryn or Phenom you just bought yesterday... Get used to the fact, this is how thing happen today. Nehalem will be probably the most advanced x86 (x64) CPU when launched, and it just happened that Intel developed it - it could have been anybody else, say AMD, or nVidia, or whoever you prefer, no difference to me. Things go ahead, and some vendors simply get the job done first, in the grand scheme of things, it is all the same. All those fanboys I see around sound like some 3 year old children fighting for candy to me, It's amusing to see how AMD or Intel PR locked you up, guys.Now a brief question, aimed directly at Anand, I guess: I still can't figure out why memory performance is so low even via an advanced controller such as Nehalem's. As far as I can tell, 3-channel DDR3-1066 should be able to deliver up to 25,5 GB/s of bandwidth, far from the figures we see. How does this happen? And once more: you measured some 46ms latency altogether, how was that obtained? Assuming memory clock of 133Mhz, this should yield something like CAS4 (~30ms) latencies for the memory, am I right?

fitten - Thursday, June 5, 2008 - link

30usAs far as single/dual/triple channel, it seems that Anand and gang were able to test with all three modes (you'll notice the comment about WinRAR being 10% faster with triple channel compared to single channel on the pre-release motherboard)... so you don't *have* to buy 3 sticks of memory... if you want 4GiB, you should be able to get 1x4 or 2x2 and leave the other slot(s) empty.

npp - Thursday, June 5, 2008 - link

It's all nanoseconds, of course, not milli- or micro, my fault. Never mind, I'm still awaiting some reasonable explanation about the "modest" bandwidth measured. 12GB/s copy is by no means little - I can't say if it's achievable via overclocking today, I'm not into that kind of business - but still I would guess no. Still, it seems little compared to the max. theoretical values.Anand Lal Shimpi - Thursday, June 5, 2008 - link

I think we may have to wait for a final Nehalem platform before we can make any calls on memory bandwidth figures, but do keep in mind that the amount of usable memory bandwidth will depend largely on how it's being measured. If the algorithm is even slightly compute bound we won't see perfect scaling with theoretical memory bandwidth.I'm not sure how Everest measures bandwidth so I can't tell you exactly what numbers we should be seeing there, but it is useful for comparing a relative increase in bandwidth between Penryn and Nehalem.

Take care,

Anand

npp - Thursday, June 5, 2008 - link

Thank you very much, very kind of you to bother answering my question! Keep up the good work here at Anandtech.NINaudio - Thursday, June 5, 2008 - link

I'm not sure hwy everyone is so concerned about DDR3 prices being high. A quick check shows that you can get a 2gig kit of ddr3-1600 for under $150 already. By the time Nehalem is out for mass consumption ddr3 will be even cheaper. I would say that it's pretty realistic to expect to be able to get a 3gig triple channel kit for under $100 and a 6gig triple channel kit for around $175 by the time nehalem is available to us.Anand Lal Shimpi - Thursday, June 5, 2008 - link

What I'm really interested in is why Intel felt that Nehalem needed a three channel DDR3 memory controller. Will it really be necessary for higher clocked Nehalem (or is it Nehalems)? It'd be great for the versions of Nehalem with integrated graphics but I figured those would mostly be pushed into the mainstream, dual channel SKUs anyways. Looks like we'll have to wait at least a few more months before we can find out for sure.-A